|                                    | The Causes of Software Defects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

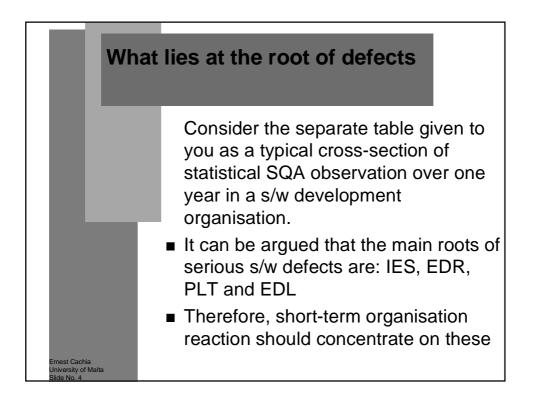

| Ernest Cachia<br>University of Mal | <ul> <li>Incomplete or erroneous spec. (IES)</li> <li>Misinterpretation of customer comm. (MCC)</li> <li>Intentional deviation from spec. (IDS)</li> <li>Violation of programming standards (VPS)</li> <li>Error in data representation (EDR)</li> <li>Inconsistent module interface (IMI)</li> <li>Error in design logic (EDL)</li> <li>Incomplete or erroneous testing (IET)</li> <li>Incomplete or inaccurate documentation (IID)</li> <li>Programming language translation of design error (PLT)</li> <li>Ambiguous or inconsistent HCI (HCI)</li> <li>Miscellaneous (MIS)</li> </ul> |

| Corrective measure examples                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Ernest Cachia<br>University of Malta<br>Slide No. 5 | <ul> <li>IES - Improve specification<br/>techniques, introduce new methods,<br/>upgrade personnel, etc.</li> <li>EDR - Adopt automated data design<br/>tools, impose stringent data modelling<br/>and reviews, etc.</li> <li>PLT - use more visibility, check<br/>design phase output, enforce strict<br/>translation techniques, etc.</li> <li>EDL - reinforce good requirements<br/>understanding, ensure personnel<br/>quality, adopt widespread design<br/>techniques, etc.</li> </ul> |  |

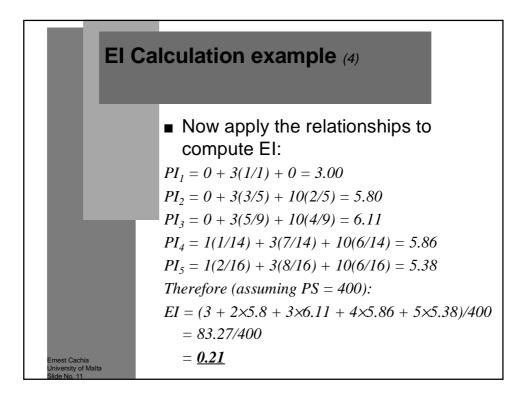

| EI                                 | Calculation example (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

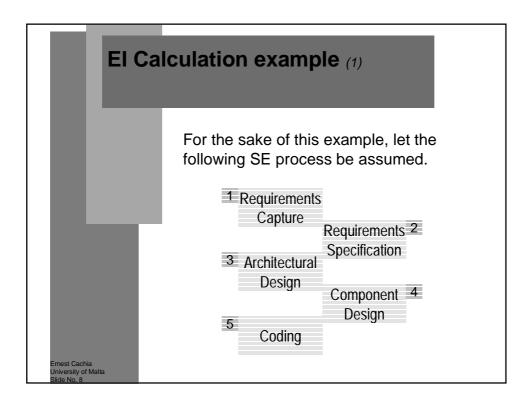

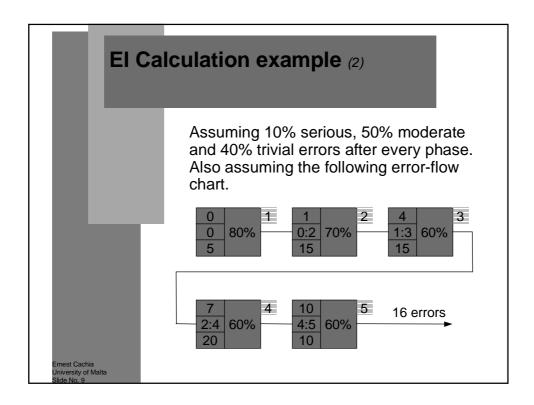

| Emest Cachia<br>University of Mata | <ul> <li>Error breakdown after each phase:         <ul> <li>1: Requirements capture</li> <li>1 error: 0 serious / 1 moderate / 0 trivial</li> </ul> </li> <li>2: Requirements specification         <ul> <li>5 errors: 0 serious / 3 moderate / 2 trivial</li> <li>3: Architectural design</li> <li>9 errors: 0 serious / 5 moderate / 4 trivial</li> <li>4: Component design                <ul> <li>14 errors: 1 serious / 7 moderate / 6 trivial</li> <li>5: Coding</li> <li>16 errors: 2 serious / 8 moderate / 6 trivial</li> </ul> </li> </ul></li></ul> |