### **Lab Experiment #10**

## **Building digital logic circuits using Decoders**

#### **Objectives**

• To learn how to build combinational logic circuits using decoders.

#### **Background**

In a **Combinational Logic Circuit**, the output is dependant at all times on the combination of its inputs. Some examples of a combinational circuit include **Multiplexers**, **De-multiplexers**, **Encoders**, **Full** and **Half Adders** etc.

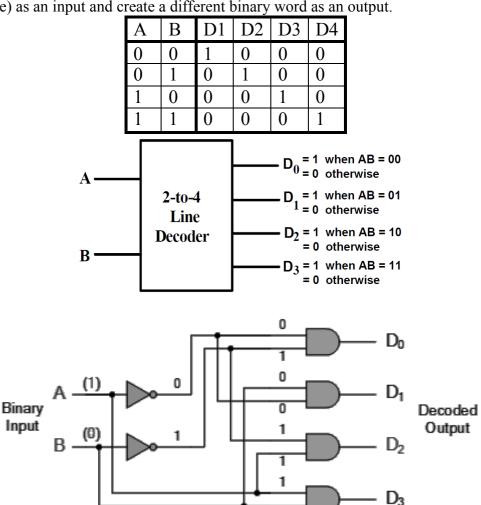

**A Decoder** is a circuit with two or more inputs and one or more outputs. Its basic function is to accept a binary word (code) as an input and create a different binary word as an output.

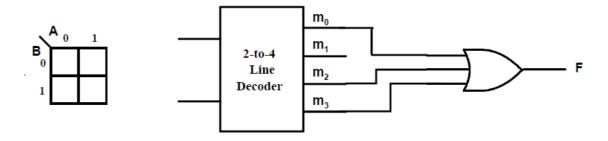

#### **Logic Functions Realized with Decoders:**

### **Drawing Decoders using EWB:**

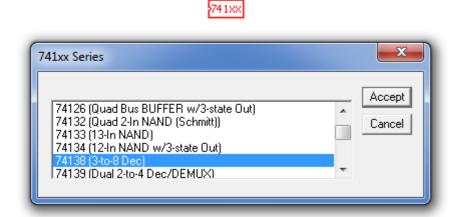

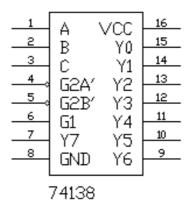

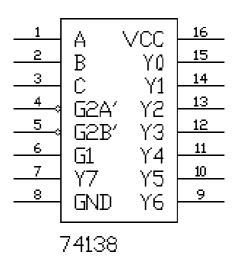

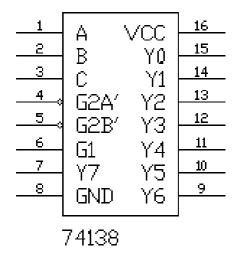

Click on the button on the toolbar, then drag a 741xx digital IC into your workspace. From the list, select either 74138 (3-8 decoder) or 74154 (4-16 decoder) as shown next.

74138 (3-8 decoder)

The 3-to-8 decoder truth table is shown next:

|      |    |      | Sele | ct |   |               |        |        |        |         |        |         |     |

|------|----|------|------|----|---|---------------|--------|--------|--------|---------|--------|---------|-----|

| G2A' | G1 | G2B' | С    | В  | A | Y0            | Y1     | Y2     | Y3     | Y4      | Y5     | Y6      | Y7  |

| X    | X  | 1    | X    | X  | X | 1             | 1      | 1      | 1      | 1       | 1      | 1       | 1   |

| X    | 0  | X    | X    | X  | X | 1             | 1      | 1      | 1      | 1       | 1      | 1       | 1   |

| 0    | 1  | 0    | 0    | 0  | 0 | 0             | 1      | 1      | 1      | 1       | 1      | 1       | 1   |

| 0    | 1  | 0    | 0    | 0  | 1 | 1             | 0      | 1      | 1      | 1       | 1      | 1       | 1   |

| 0    | 1  | 0    | 0    | 1  | 1 | 1             | 1      | 0      | 1      | 1       | 1      | 1       | 1   |

| 0    | 1  | 0    | 0    | 1  | 1 | 1             | 1      | 1      | 0      | 1       | 1      | 1       | 1   |

| 0    | 1  | 0    | 1    | 0  | 0 | 1             | 1      | 1      | 1      | 0       | 1      | 1       | 1   |

| 0    | 1  | 0    | 1    | 0  | 1 | 1             | 1      | 1      | 1      | 1       | 0      | 1       | 1   |

| 0    | 1  | 0    | 1    | 1  | 0 | 1             | 1      | 1      | 1      | 1       | 1      | 0       | 1   |

| 0    | 1  | 0    | 1    | 1  | 1 | 1             | 1      | 1      | 1      | 1       | 1      | 1       | 0   |

| 1    | 1  | 0    | X    | X  | X | Outp<br>other | ut con | respon | ding t | o store | ed add | ress 0; | all |

74154 (4-16 decoder)

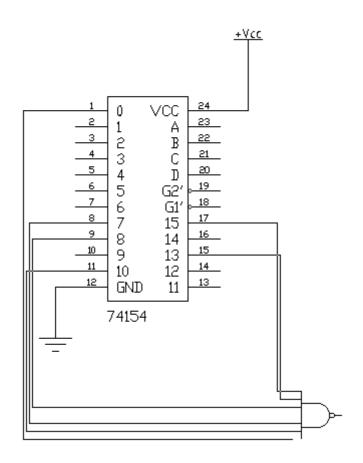

## Example: drawing a 4-input function using 74154 (Sum of minterms)

Next is the function  $F(D, C, B, A)=\Sigma 0$ , 7, 8, 10, 13, 15

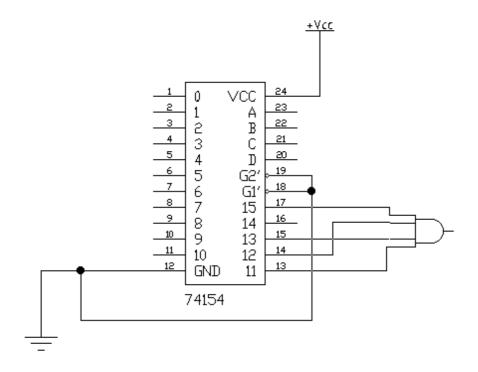

# Example: drawing a 4-input function using 74154 (Product of maxterms)

Next is the function  $F(D, C, B, A) = \Pi 11, 12, 13, 15$

## Lab Tasks

Task 1: Implementing 3-variable Boolean expressions using 3-8 decoder

Implement the following function using 3-8 decoders.

|   | A | В | C | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 0 | 1 | 1 | 1 |

| 4 | 1 | 0 | 0 | 1 |

| 5 | 1 | 0 | 1 | 0 |

| 6 | 1 | 1 | 0 | 0 |

| 7 | 1 | 1 | 1 | 0 |

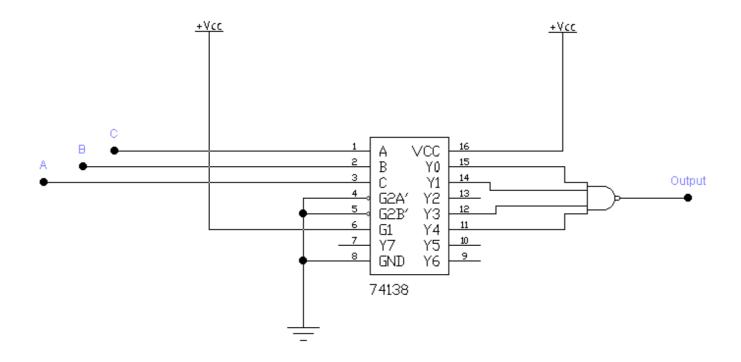

The above function can be implemented as shown next. Redraw this circuit using EWB.

Task 2: Implementing multiple 3-variable Boolean expressions using 3-8 decoder Implement the following three functions using 3-8 decoders.

|   | A | В | C | F1 | F2 | F3 |

|---|---|---|---|----|----|----|

| 0 | 0 | 0 | 0 | 0  | 1  | 1  |

| 1 | 0 | 0 | 1 | 1  | 1  | 0  |

| 2 | 0 | 1 | 0 | 0  | 0  | 1  |

| 3 | 0 | 1 | 1 | 1  | 1  | 0  |

| 4 | 1 | 0 | 0 | 0 | 1 | 1 |

|---|---|---|---|---|---|---|

| 5 | 1 | 0 | 1 | 1 | 0 | 0 |

| 6 | 1 | 1 | 0 | 1 | 0 | 0 |

| 7 | 1 | 1 | 1 | 0 | 0 | 1 |

Task 3: Problems with verbal description

Design a combinational circuit (using **one 4-16 decoder**) with four inputs, and one output to implement the following function.

|    | A | В | C | D | F |

|----|---|---|---|---|---|

| 0  | 0 | 0 | 0 | 0 | 0 |

| 1  | 0 | 0 | 0 | 1 | 1 |

| 2  | 0 | 0 | 1 | 0 | 0 |

| 3  | 0 | 0 | 1 | 1 | 1 |

| 4  | 0 | 1 | 0 | 0 | 0 |

| 5  | 0 | 1 | 0 | 1 | 0 |

| 6  | 0 | 1 | 1 | 0 | 1 |

| 7  | 0 | 1 | 1 | 1 | 1 |

| 8  | 1 | 0 | 0 | 0 | 1 |

| 9  | 1 | 0 | 0 | 1 | 0 |

| 10 | 1 | 0 | 1 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 |

| 13 | 1 | 1 | 0 | 1 | 0 |

| 14 | 1 | 1 | 1 | 0 | 0 |

| 1.5 | 1 | 1 | 1 | 1 | 1 |

|-----|---|---|---|---|---|

| 15  | 1 | 1 | 1 | 1 | 1 |

|     |   |   |   |   |   |

| 4 3 C 21<br>5 4 D 20<br>6 5 G2′ № 19<br>7 6 G1′ № 18                                                                                            |                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2 1 A 23<br>3 2 B 22<br>4 3 C 21<br>5 4 D 20<br>6 5 G2' 19<br>7 6 G1' 18<br>8 7 15 17<br>9 8 14 16<br>10 9 13 15<br>11 10 12 14<br>12 GND 11 13 | 15 17<br>14 16<br>13 15<br>12 14 |

Task 4: Problems with verbal description

Design a combinational circuit (using **two 3-8 decoder**) with four inputs, and one output to implement the following function.

|    | A | В | C | D | F |

|----|---|---|---|---|---|

| 0  | 0 | 0 | 0 | 0 | 0 |

| 1  | 0 | 0 | 0 | 1 | 1 |

| 2  | 0 | 0 | 1 | 0 | 0 |

| 3  | 0 | 0 | 1 | 1 | 1 |

| 4  | 0 | 1 | 0 | 0 | 0 |

| 5  | 0 | 1 | 0 | 1 | 0 |

| 6  | 0 | 1 | 1 | 0 | 1 |

| 7  | 0 | 1 | 1 | 1 | 1 |

| 8  | 1 | 0 | 0 | 0 | 1 |

| 9  | 1 | 0 | 0 | 1 | 0 |

| 10 | 1 | 0 | 1 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 |

| 13 | 1 | 1 | 0 | 1 | 0 |

| 14 | 1 | 1 | 1 | 0 | 0 |

| 15 | 1 | 1 | 1 | 1 | 1 |

16\_\_\_ 1 VCC Α 2 15 В ΥŌ 3 14 Y1 4 13 G2A′ Y2 5 12 G2B'YЗ 6 11 G1 Y4 7 10 Y7. Y5 8 9 GND Y6. 74138